指令級并行(Instruction-Level Parallelism, ILP)是計算機體系結構中的一個關鍵概念,旨在通過同時執行多條指令來提升處理器的性能。現代計算機系統通過多種技術實現指令級并行,包括流水線處理、超標量架構、亂序執行和動態調度等。這些技術使得處理器能夠在單個時鐘周期內執行多個操作,從而顯著提高指令吞吐量。

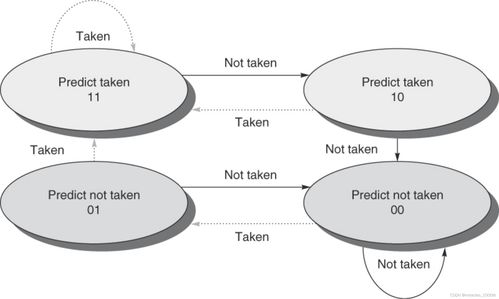

在計算機體系結構中,指令級并行的實現依賴于硬件和軟件的緊密協作。硬件方面,處理器設計采用多功能單元、分支預測和寄存器重命名等技術,以減少指令間的依賴關系,最大化并行執行的機會。軟件方面,編譯器通過指令調度和循環展開等優化手段,重新組織代碼順序,以更好地利用處理器的并行能力。

指令級并行也面臨挑戰,如數據依賴、控制依賴和資源沖突等問題,這些都可能限制并行的效果。例如,數據依賴要求某些指令必須按順序執行,而分支指令可能導致流水線停頓。為了克服這些限制,現代處理器引入了推測執行和動態優化機制,在運行時調整指令流。

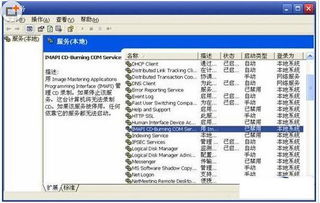

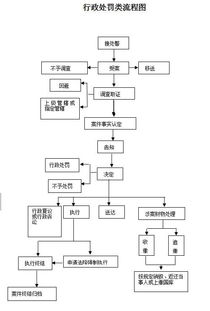

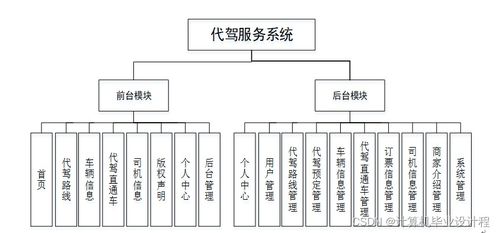

計算機系統服務在支持指令級并行方面扮演著重要角色。操作系統通過進程調度、內存管理和中斷處理等服務,確保多任務環境下的資源公平分配和高效利用。例如,虛擬內存機制允許程序訪問更大的地址空間,而緩存管理服務則優化數據訪問速度,減少處理器等待時間。系統調用和驅動程序提供硬件抽象,使得應用程序能夠無縫利用底層并行架構,而無需直接處理復雜的硬件細節。

指令級并行是提升計算機性能的核心技術之一,其成功實現離不開計算機體系結構的創新和計算機系統服務的支持。隨著技術的發展,如多核處理器和異構計算的出現,指令級并行繼續演化,并與線程級并行和任務級并行結合,推動著計算效率的持續提升。隨著人工智能和物聯網等應用的普及,優化指令級并行和系統服務將變得更加關鍵,以滿足日益增長的計算需求。